从锁存器到RAM

当电路中输出和输入相关时,我们就有机会得到带有存储功能的电路了,最简单的例子是SR锁存器。

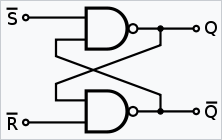

SR锁存器

分析该电路时,我们从确定性的角度出发,对于与非门,任何一端输入0,结果一定是1。那么我们很容易知道,(S, R) = (0, 1), (1, 0), (1, 1)的情况。但当其为(0, 0)时,其保持上一阶段的状态,这就起到了保存一位数据的作用。

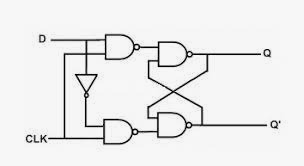

D触发器

为了解决多个SR触发器无法同时动作以及SR触发器(1, 1)为非法状态的问题,我们引入D触发器,其电路示意图如下。

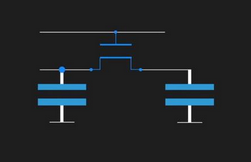

SRAM

由此,我们就可以构建RAM了,也就是我们所说的内存或者Cache。其基本结构是MOS管,通过行选和列选信号确定一bit的数据,并通过读写控制信号控制读或者写。

一共用了8个MOS管,速度非常快,但是集成度做不上去,因此只用在Cache上。

DRAM

为了提高集成度,我们使用电容做数据存储的媒介,MOS管作为开关。但电容会缓慢放电,因此为了维持数据,其需要不断被补充电荷,这个过程就是刷新。因此这种RAM被称为动态RAM,DRAM用于内存。

参考来源:B站Ele实验室

-------------本文结束感谢您的阅读-------------